# Analysis of the Switching Characteristics of GaN HEMTs Using Double-Pulse Test and a Buck

**Converter** by Rafael García Villa

Author

## Analysis of the Switching Characteristics of GaN HEMTs Using Double-Pulse Test and a Buck Converter

by

Rafael García Villa

Submitted to the Department of Electrical Engineering, Electronics, Computers and Systems on November 21, 2018, in partial fulfillment of the requirements for the degree of Master Course in Electrical Energy Conversion and Power Systems

#### Abstract

In this thesis, the rising and promising switching power technology of the *Gallium* Nitride (GaN) transistors will be studied. It has been observed that the evolution of Silicon (Si) transistors has almost reached its theoretical limits, so new technologies are being studied to find new improvements that allow the power conversion field to continue developing and increasing.

During this project, the aforementioned GaN technology will be evaluated in several ways. First, a deep theoretical study will be carried out, explaining the main characteristics of these devices. Then, a set of tests will be performed to analyse the behaviour of the GaN transistors, which include the double-pulse test and a synchronous buck converter. In both cases, the power devices will be evaluated experimentally and in simulations, in order to compare both results. During the tests, different operating points will be studied (different voltages and current levels). To carry out these analyses experimentally, an evaluation kit of *GaN Systems* will be employed, as well as a Digital Signal Processor (DSP) of *Texas Instruments* to control the commutation of the devices. In the case of the simulations, the latest version of the simulating program *PSIM* will be used, which allows to include the real behaviour of the power devices.

The obtained results will be exposed and commented, trying to identify the particularities of these devices and making a comparison between the simulation and experimental results.

Thesis Supervisor: Giulio De Donato Title: Associate Professor

Thesis Supervisor: Jorge García García Title: Associate Professor

# Contents

| 1        | 1 Introduction |         |                                                    |    |  |

|----------|----------------|---------|----------------------------------------------------|----|--|

|          | 1.1            | Proble  | em Background                                      | 15 |  |

|          | 1.2            | Objec   | tive of the Thesis and Report Outline              | 16 |  |

| <b>2</b> | Gal            | lium-N  | Nitride HEMTs                                      | 19 |  |

|          | 2.1            | Mater   | ial Properties and Advantages of GaN               | 19 |  |

|          | 2.2            | Funda   | amentals of 2DEG and HEMTs                         | 22 |  |

|          | 2.3            | The E   | Basic Device Structure                             | 24 |  |

|          |                | 2.3.1   | Recessed Gate Enhancement-Mode Structure           | 26 |  |

|          |                | 2.3.2   | Implanted Gate Enhancement-Mode Structure          | 27 |  |

|          |                | 2.3.3   | Cascode Hybrid Enhancement-Mode Structure          | 27 |  |

|          | 2.4            | GaN I   | HEMTs Electrical Characteristics                   | 28 |  |

|          |                | 2.4.1   | Breakdown Voltage $V_{BD}$                         | 28 |  |

|          |                | 2.4.2   | On-Resistance $R_{DS(on)}$                         | 29 |  |

|          |                | 2.4.3   | Threshold Voltage $V_{th}$                         | 32 |  |

|          |                | 2.4.4   | Parasitic Capacitances                             | 33 |  |

|          |                | 2.4.5   | Reverse Conduction of HEMTs                        | 34 |  |

|          | 2.5            | Gate I  | Drive Voltage Considerations                       | 35 |  |

| 3        | The            | eoretic | al Frame of the Analyses                           | 39 |  |

|          | 3.1            | Doubl   | e-Pulse Test                                       | 39 |  |

|          |                | 3.1.1   | Theoretical Background of the Double-Pulse Test    | 39 |  |

|          |                | 3.1.2   | Simulation Implementation of the Double-Pulse Test | 41 |  |

|          |     | 3.1.3   | Experimental Implementation of the Double-Pulse Test $% \mathcal{A} = \mathcal{A} = \mathcal{A} + \mathcal{A}$ | 42   |

|----------|-----|---------|----------------------------------------------------------------------------------------------------------------|------|

|          |     | 3.1.4   | Characteristics of the GS66516B HEMTs                                                                          | 50   |

|          |     | 3.1.5   | Tests with the Signal Generation Source                                                                        | 53   |

|          |     | 3.1.6   | Tests with the DSP                                                                                             | 55   |

|          | 3.2 | Buck (  | Converter                                                                                                      | 59   |

|          |     | 3.2.1   | Operation of a Buck Converter                                                                                  | 59   |

|          |     | 3.2.2   | Synchronous Buck Converter                                                                                     | 62   |

|          |     | 3.2.3   | Design of the Buck Converter                                                                                   | 64   |

|          |     | 3.2.4   | Dead-Time Generation                                                                                           | 68   |

|          |     | 3.2.5   | Simulation Implementation of the Synchronous Buck Converter                                                    | 69   |

|          |     | 3.2.6   | Experimental Implementation of the Synchronous Buck Converter                                                  | : 73 |

| 4        | Exp | perime  | ntal and Simulation Results                                                                                    | 83   |

|          | 4.1 | Double  | e-Pulse Test                                                                                                   | 84   |

|          |     | 4.1.1   | Transient Analyses for the DPTs                                                                                | 85   |

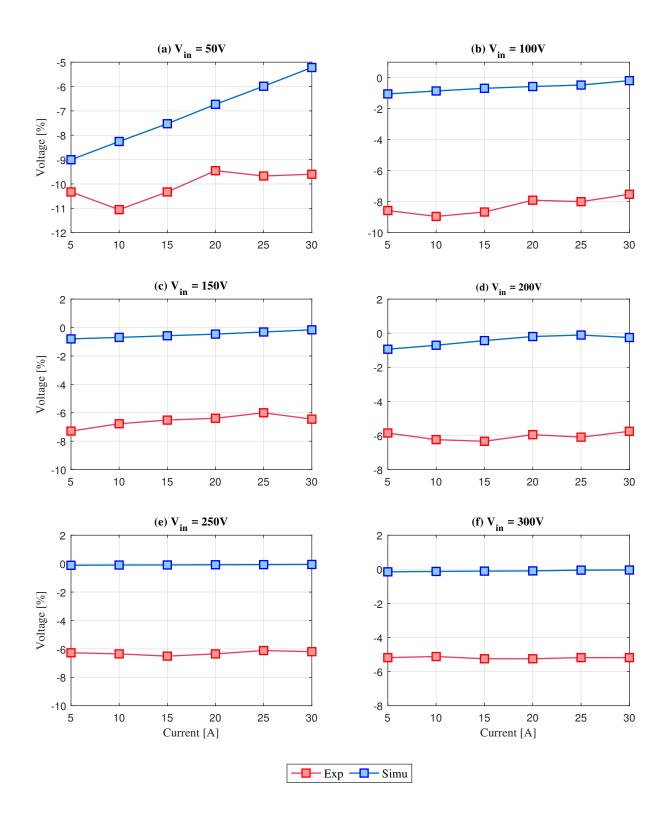

|          |     | 4.1.2   | Peak voltages produced at the turn-off and turn-on events $\ . \ .$                                            | 92   |

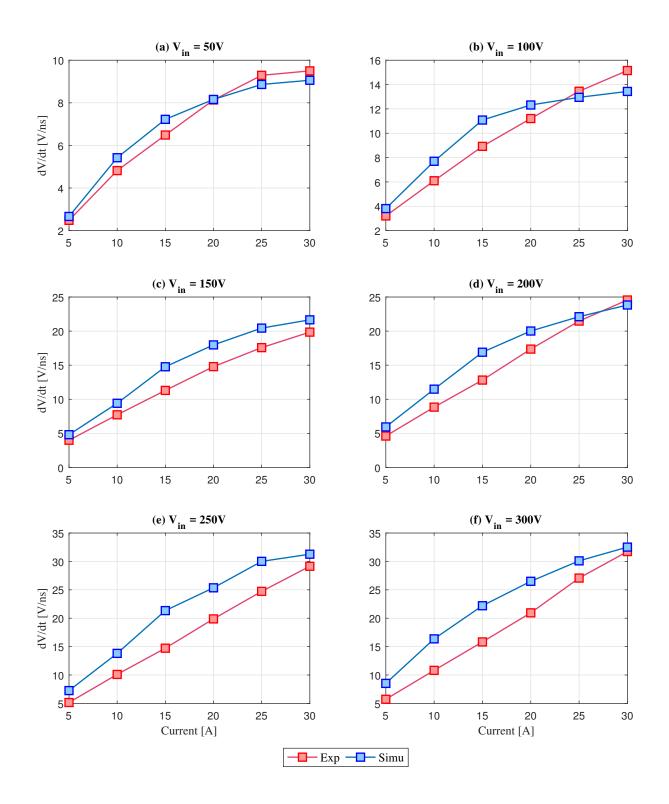

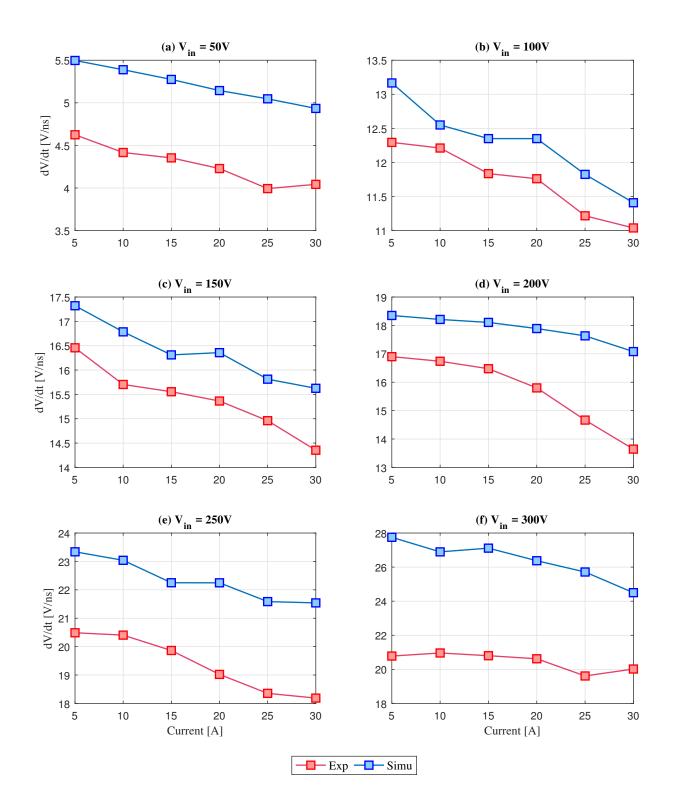

|          |     | 4.1.3   | $\mathrm{d}V/\mathrm{d}t$ produced at the turn-off and turn-on events $\ .$                                    | 96   |

|          | 4.2 | Synch   | ronous Buck Converter Test                                                                                     | 99   |

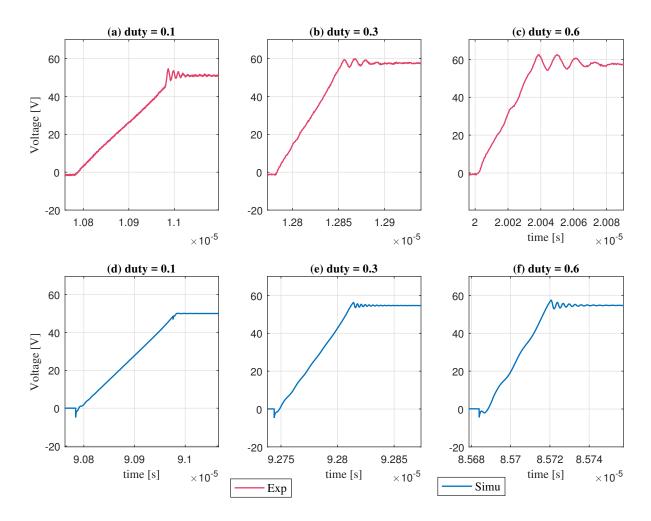

|          |     | 4.2.1   | Transient analyses for the Synchronous Buck Converter                                                          | 100  |

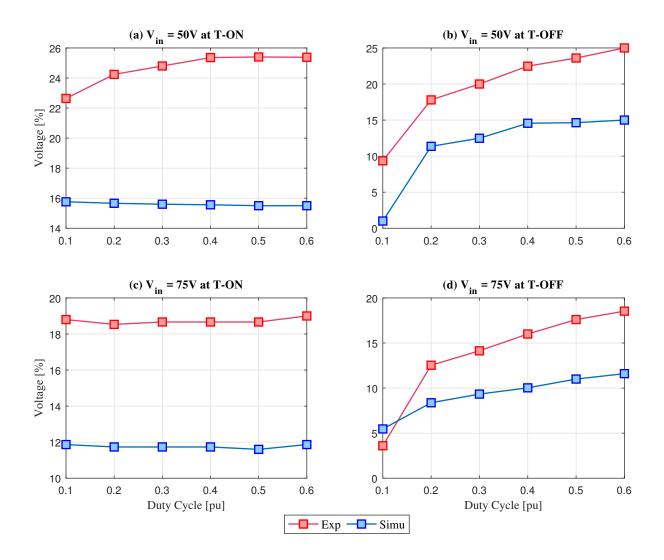

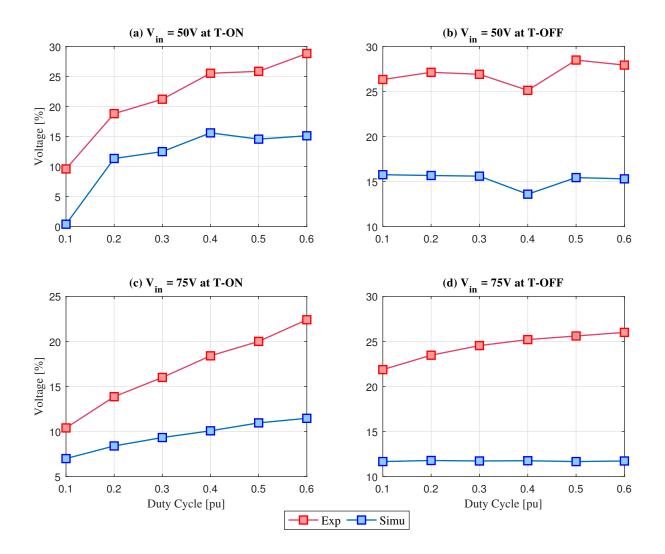

|          |     | 4.2.2   | Peak voltages produced at the turn-off and turn-on events $\ . \ .$                                            | 105  |

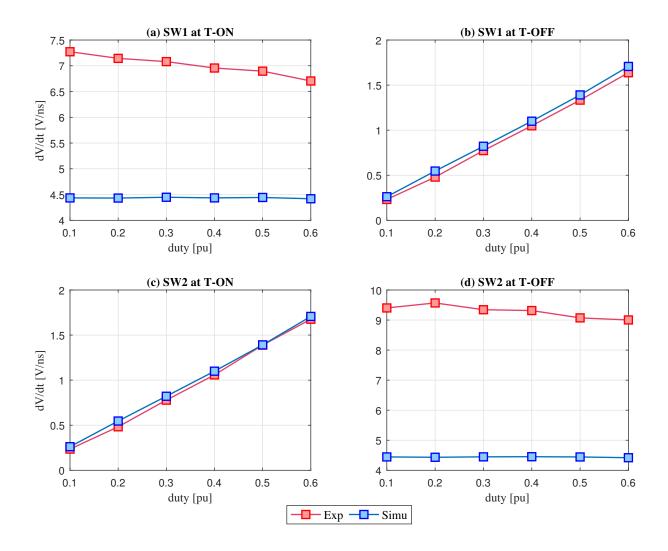

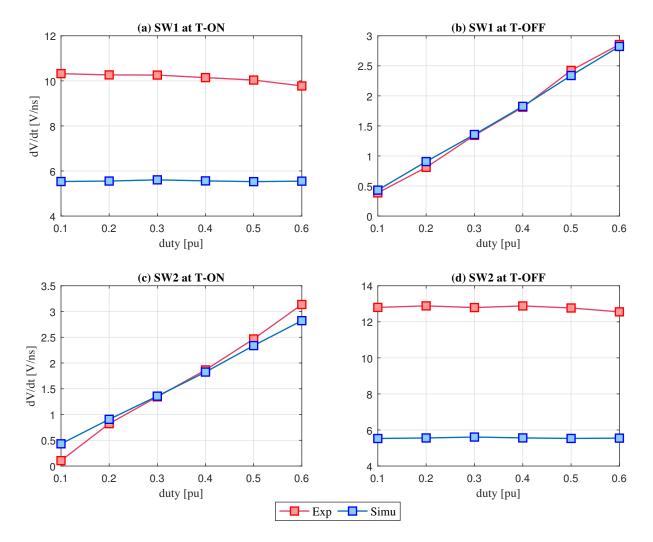

|          |     | 4.2.3   | $\mathrm{d}V/\mathrm{d}t$ produced at the turn-on and turn-off events $\ .$                                    | 108  |

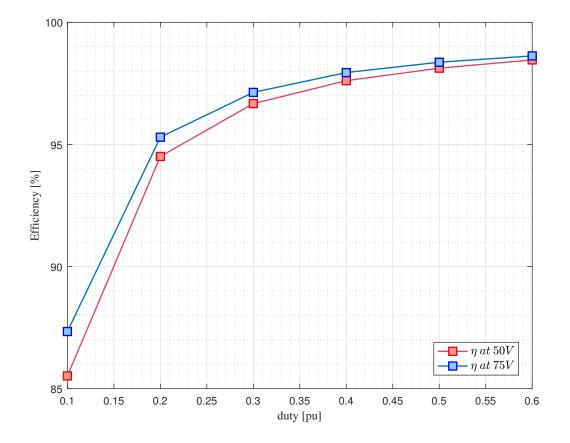

|          |     | 4.2.4   | Analysis of the Synchronous-Buck Efficiency                                                                    | 111  |

|          |     | 4.2.5   | Comparison of the Synchronous Buck-Converter Efficiency: GaN                                                   |      |

|          |     |         | vs Si                                                                                                          | 112  |

| <b>5</b> | Cor | nclusio | ns and Future Work                                                                                             | 115  |

|          | 5.1 | Conclu  | isions                                                                                                         | 115  |

|          |     | 5.1.1   | Double-Pulse Tests                                                                                             | 115  |

|          |     | 5.1.2   | Synchronous Buck Converter Tests                                                                               | 116  |

|          | 5.2 | Future  | e Work                                                                                                         | 117  |

# List of Figures

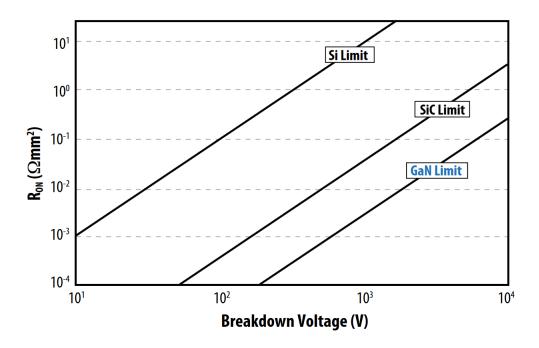

| 2-1  | Theoretical on-resistance vs blocking voltage capability for silicon, silicon-            |    |

|------|-------------------------------------------------------------------------------------------|----|

|      | carbide, and gallium nitride [3]                                                          | 21 |

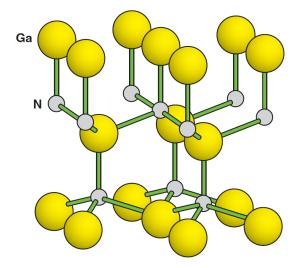

| 2-2  | Schematic of wurtzite GaN [27]                                                            | 23 |

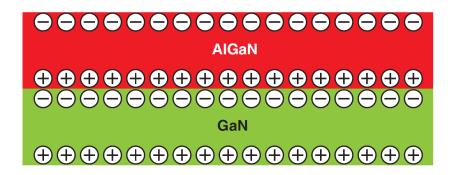

| 2-3  | Simplified cross section of a GaN/AlGaN heterostructure showing the                       |    |

|      | formation of a 2DEG due to the strain-induced polarization at the                         |    |

|      | interface between the two materials [27]                                                  | 24 |

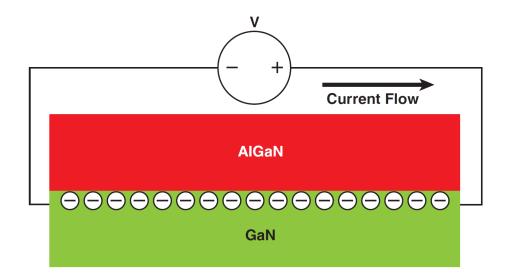

| 2-4  | By applying a voltage to the 2DEG an electric current is induced in                       |    |

|      | the crystal [27]. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 24 |

| 2-5  | By applying a negative voltage to the gate of the device, the electrons                   |    |

|      | in the 2DEG are depleted out of the device. This type of device is                        |    |

|      | called a depletion-mode (d-mode) HEMT [27]                                                | 25 |

| 2-6  | (a) An enhancement-mode (e-mode) device depletes the 2DEG with                            |    |

|      | zero volts on the gate. (b) By applying a positive voltage to the gate,                   |    |

|      | the electrons are attracted to the surface, re-establishing the 2DEG $\left[ 27\right] .$ | 26 |

| 2-7  | Cascode configuration combining a high voltage normally on GaN                            |    |

|      | HEMT with a low voltage normally off silicon MOSFET                                       | 27 |

| 2-8  | The device in Figure 2.6 showing the electric fields when voltage is                      |    |

|      | applied from drain to source                                                              | 29 |

| 2-9  | Cross section of a GaN HEMT, showing the major components of                              |    |

|      | $R_{DS(on)}$ [27]                                                                         | 30 |

| 2-10 | Normalized $R_{DS_{ON}}$ vs. temperature for a 100V enhancement-mode                      |    |

|      | GaN transistor (EPC2010) compared with an Si power MOSFET with                            |    |

|      | similar ratings [39]                                                                      | 31 |

| 2-11 | Schematic of GaN transistor capacitive sources [27]                                      | 33 |

|------|------------------------------------------------------------------------------------------|----|

| 2-12 | Body-diode forward drop vs. source-drain current and temperature by                      |    |

|      | EPC2010 [39]                                                                             | 34 |

| 2-13 | Gate charge vs. gate voltage showing different gate charge components                    |    |

|      | for an EPC2010 GaN transistor [39].                                                      | 37 |

| 3-1  | Double-pulse test circuit - Inductive load                                               | 40 |

| 3-2  | Double-pulse test signals - Inductive load.                                              | 41 |

| 3-3  | (a) GS66508T/GS66516T-EVBDB GaN E-HEMT top side daughter                                 |    |

|      | board 650V. (b) GS665MB-EVB Evaluation Platform                                          | 43 |

| 3-4  | First assembly used to perform the double-pulse test                                     | 44 |

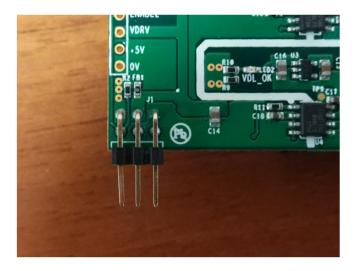

| 3-5  | Poor pin connectors used to transmit the control signals from the                        |    |

|      | mother board (connected with the pulse source generator) to the daugther $% \mathcal{A}$ |    |

|      | board                                                                                    | 45 |

| 3-6  | Experimental Evaluation Kit: GSP65RxxHB evaluation motherboard                           |    |

|      | and $650V$ high power insulated metal substrate (IMS) evaluation mod-                    |    |

|      | ules                                                                                     | 46 |

| 3-7  | Insulated metal substrate (IMS) evaluation module used in the moth-                      |    |

|      | erboard                                                                                  | 47 |

| 3-8  | Pin connectors used to transmit the pulse signals to the gate drivers                    |    |

|      | of the GaN HEMTs from the mother<br>board to the IMS. $\ldots$ . $\ldots$ .              | 49 |

| 3-9  | (a) SMD package for the used GaN HEMTs. (b) Terminals of the used                        |    |

|      | GaN HEMTs in relation with (c), which shows the electrical symbol                        |    |

|      | representation of the trnasistor                                                         | 51 |

| 3-10 | Assembly used to create the required double pulses to perform the                        |    |

|      | double-pulse test with the signal generator and the OR gate                              | 54 |

| 3-11 | (a) Commands produced by the generator source channels. (b) Pulses                       |    |

|      | produced by combining the signal generator commands and the OR gate.                     | 55 |

| 3-12 | Flow chart of the program created to generate the pulses for the double-                 |    |

|      | pulse test.                                                                              | 58 |

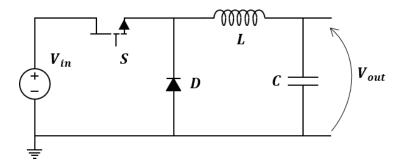

| 3-13 | Electrical scheme of the buck converter                                       | 59 |

|------|-------------------------------------------------------------------------------|----|

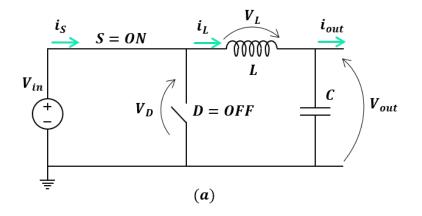

| 3-14 | Equivalent circuit of the buck converter when operating in CCM: (a)           |    |

|      | Switch = $ON$ and $Diode = OFF$ ; (b) Switch = $OFF$ and $Diode = ON$ .       | 60 |

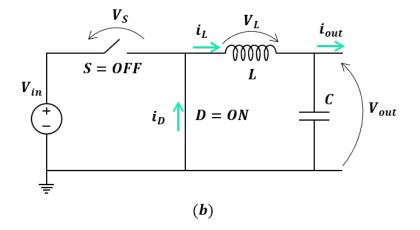

| 3-15 | Buck switching waveforms corresponding to the two possible states             |    |

|      | when operating in CCM                                                         | 62 |

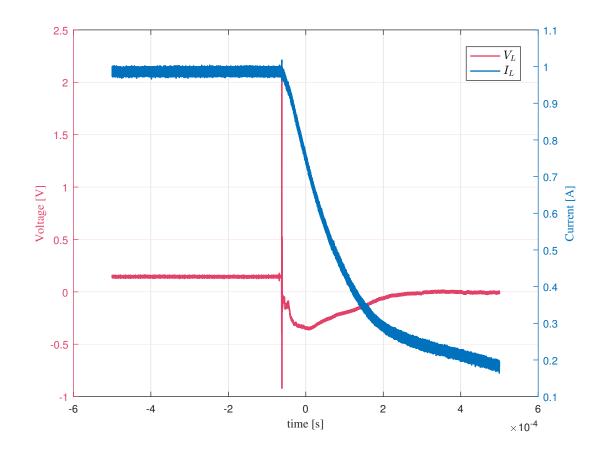

| 3-16 | Circuit used to determine the value of the available inductors                | 65 |

| 3-17 | Real circuit used to determine the value of the available inductors           | 66 |

| 3-18 | Inductor current and voltage signals obtained during the test per-            |    |

|      | formed to get the inductance value                                            | 67 |

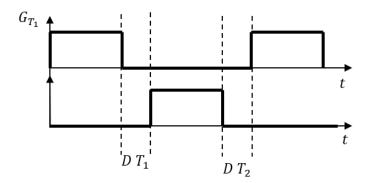

| 3-19 | Deadtimes $DT_1$ and $DT_2$ are inserted between the gating signals           | 69 |

| 3-20 | Gate drive circuit used to create the gate drive signals to control the       |    |

|      | buck converter.                                                               | 70 |

| 3-21 | Gate drive signals used to control the synchronous-buck converter             | 72 |

| 3-22 | Wrong waveforms observed during buck tests                                    | 74 |

| 3-23 | Physical assembly used for the buck converter                                 | 75 |

| 3-24 | Flow chart of the program created to generate the pulses for the buck         |    |

|      | test                                                                          | 80 |

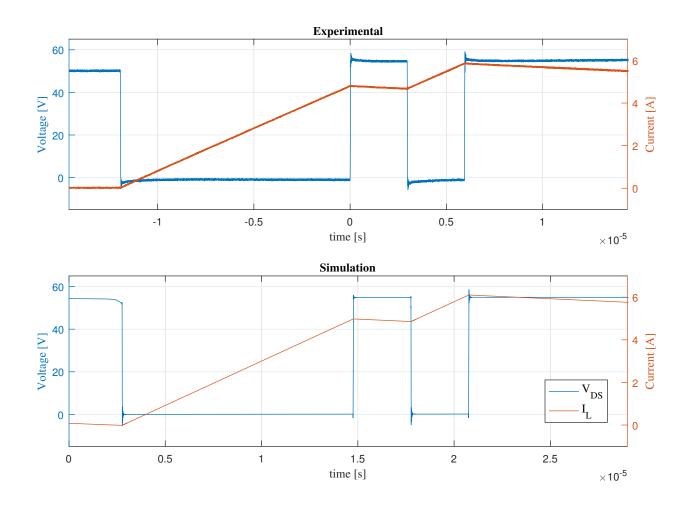

| 4-1  | Drain-to-source voltage and inductor current observed in the DPT for          |    |

|      | $V_{in} = 50V$ and $I = 5A$                                                   | 84 |

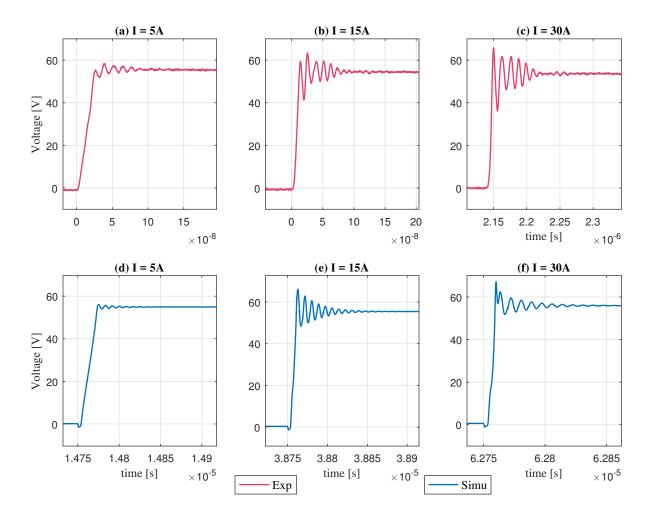

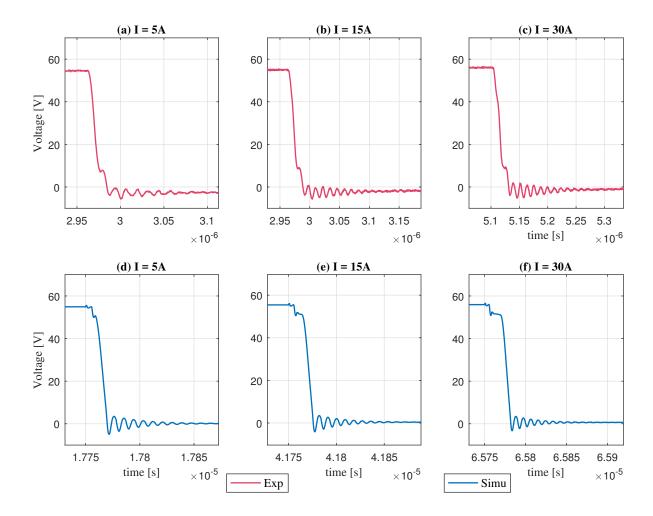

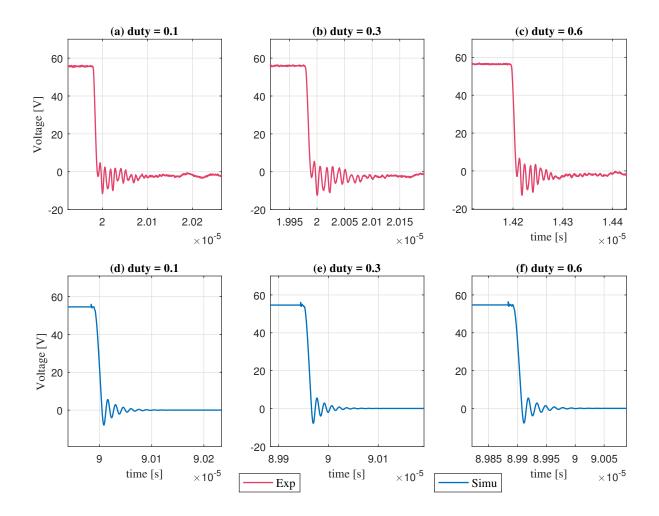

| 4-2  | Drain-to-source $(V_{DS})$ voltage transients produced at the turn-off for    |    |

|      | different current levels at $V_{in} = 50V$ : (a) Experimental at 5A; (b)      |    |

|      | Experimental at $15A$ ;(c) Experimental at $30A$ ;(d) Simulation at $5A$ ;(e) |    |

|      | Simulation at $15A$ ;(f) Simulation at $30A$                                  | 86 |

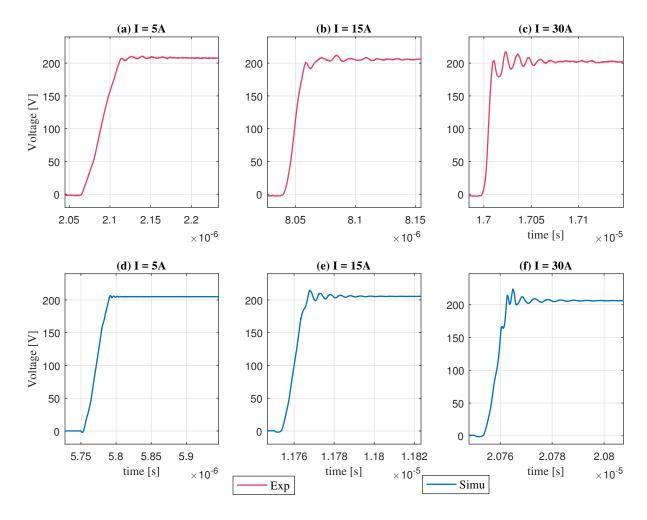

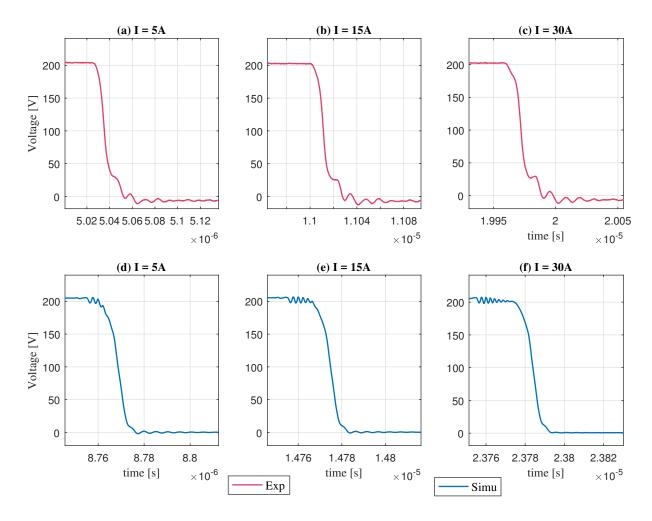

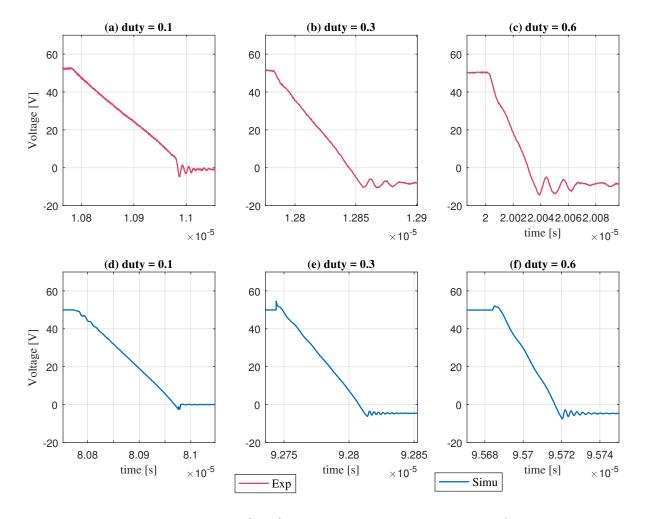

| 4-3  | Drain-to-source $(V_{DS})$ voltage transients produced at the turn-off for    |    |

|      | different current levels at $V_{in} = 200V$ : (a) Experimental at 5A; (b)     |    |

|      | Experimental at $15A$ ;(c) Experimental at $30A$ ;(d) Simulation at $5A$ ;(e) |    |

|      | Simulation at $15A$ ;(f) Simulation at $30A$                                  | 87 |

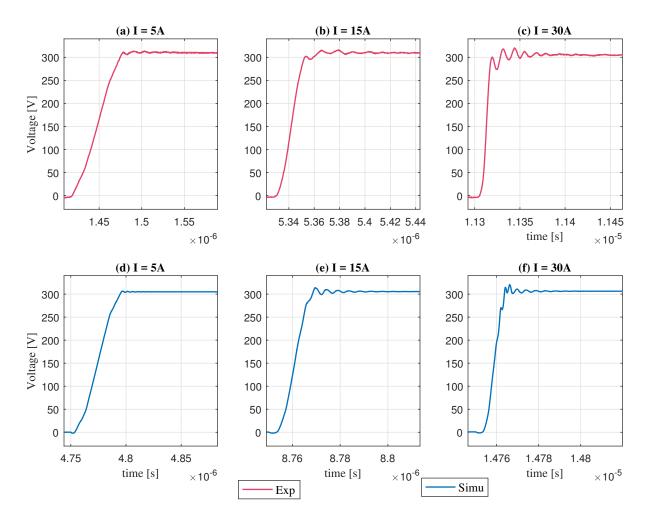

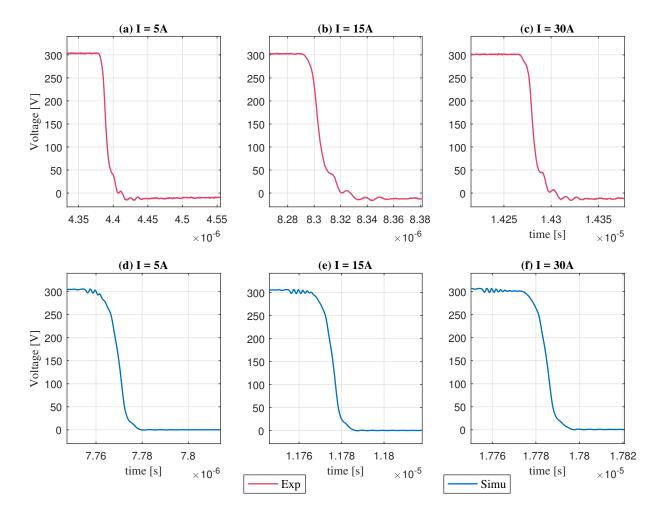

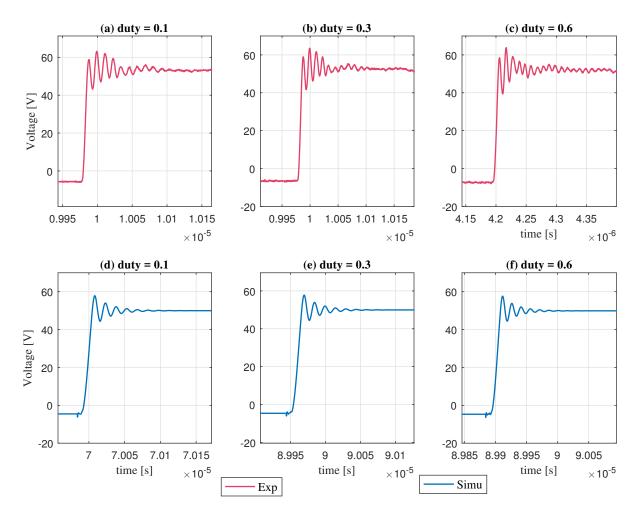

| 4-4  | Drain-to-source $(V_{DS})$ voltage transients produced at the turn-off for<br>different current levels at $V_{in} = 300V$ : (a) Experimental at 5A; (b)<br>Experimental at 15A;(c) Experimental at 30A;(d) Simulation at 5A;(e)<br>Simulation at 15A;(f) Simulation at 20A                                                                | 88 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4-5  | Simulation at $15A$ ;(f) Simulation at $30A$<br>Drain-to-source $(V_{DS})$ voltage transients produced at the turn-on for<br>different current levels at $V_{in} = 50V$ : (a) Experimental at $5A$ ; (b)<br>Experimental at $15A$ ;(c) Experimental at $30A$ ;(d) Simulation at $5A$ ;(e)<br>Simulation at $15A$ ;(f) Simulation at $30A$ | 89 |

| 4-6  | Drain-to-source $(V_{DS})$ voltage transients produced at the turn-on for<br>different current levels at $V_{in} = 200V$ : (a) Experimental at 5A; (b)<br>Experimental at 15A;(c) Experimental at 30A;(d) Simulation at 5A;(e)<br>Simulation at 15A;(f) Simulation at 30A                                                                 | 90 |

| 4-7  | Drain-to-source $(V_{DS})$ voltage transients produced at the turn-on for<br>different current levels at $V_{in} = 300V$ : (a) Experimental at 5A; (b)<br>Experimental at 15A;(c) Experimental at 30A;(d) Simulation at 5A;(e)<br>Simulation at 15A;(f) Simulation at 30A                                                                 | 91 |

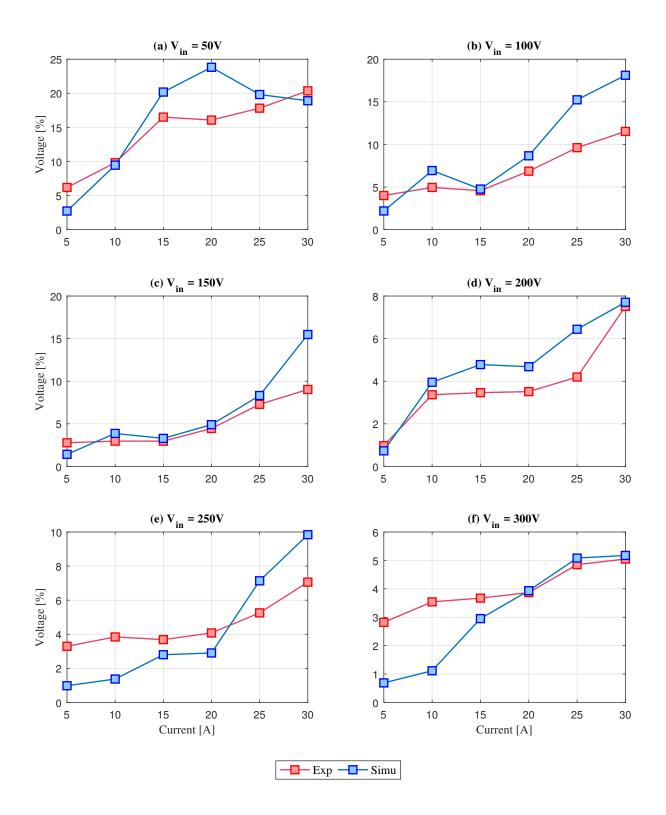

| 4-8  | Drain-to-source $(V_{DS})$ peak voltages produced at the turn-off overshoot<br>for different current levels and different test voltages: (a) $V_{in} = 50V$ ;<br>(b) $V_{in} = 50V$ ;(c) $V_{in} = 50V$ ;(d) $V_{in} = 50V$ ;(e) $V_{in} = 50V$ ;(f) $V_{in} = 50V$ .                                                                     | 93 |

| 4-9  | Drain-to-source $(V_{DS})$ peak voltages produced at the turn-on overshoot<br>for different current levels and different test voltages: (a) $V_{in} = 50V$ ;<br>(b) $V_{in} = 50V$ ;(c) $V_{in} = 50V$ ;(d) $V_{in} = 50V$ ;(e) $V_{in} = 50V$ ;(f) $V_{in} = 50V$ .                                                                      | 95 |

| 4-10 | Drain-to-source $(V_{DS}) dV/dt$ in $[V/ns]$ produced at the turn-off event<br>for different current levels and different test voltages: (a) $V_{in} = 50V$ ;<br>(b) $V_{in} = 50V$ ;(c) $V_{in} = 50V$ ;(d) $V_{in} = 50V$ ;(e) $V_{in} = 50V$ ;(f) $V_{in} = 50V$ .                                                                     | 97 |

| 4-11 | Drain-to-source $(V_{DS}) dV/dt$ in $[V/ns]$ produced at the turn-on event<br>for different current levels and different test voltages: (a) $V_{in} = 50V$ ;<br>(b) $V_{in} = 50V$ ;(c) $V_{in} = 50V$ ;(d) $V_{in} = 50V$ ;(e) $V_{in} = 50V$ ;(f) $V_{in} = 50V$ .                                                                      | 98 |

###

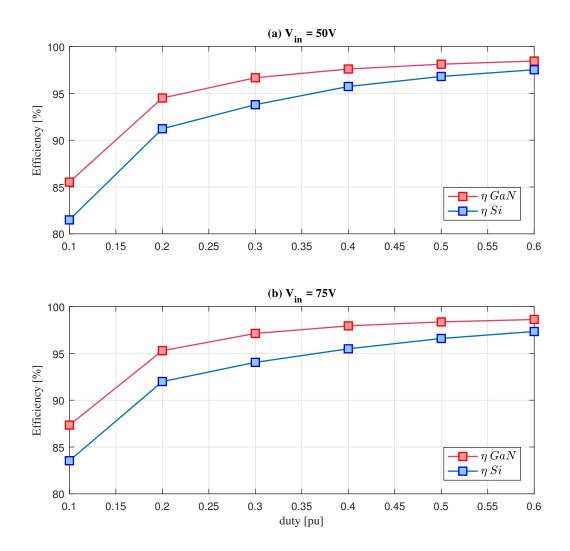

- 4-21 Efficiency of the synchornous buck converter obtained in the simulations for different input voltage levels at different duty cycles. . . . . 111

- 4-22 Comparison of the synchornous buck converter efficiency obtained in the simulations when using GaN and Si technology for different input voltage levels at different duty cycles.

113

# List of Tables

| 2.1 | Material properties of Si, SiC and GaN [26]                                  | 20 |

|-----|------------------------------------------------------------------------------|----|

| 2.2 | Figures of merit of GaN and competing semiconductor materials in             |    |

|     | power electronics [5]. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 21 |

| 2.3 | Gate drive voltages for GaN HEMTs, Si MOSFET, IGBT and SiC                   |    |

|     | MOSFEt [48]                                                                  | 38 |

|     |                                                                              |    |

| 3.1 | Parameters used for the DPT simulations                                      | 42 |

| 3.2 | Parameters used for the DPT simulations.                                     | 50 |

# Chapter 1

# Introduction

### 1.1 Problem Background

During the last thirty years, metal oxide silicon field effect transistors (MOSFETs) have experienced a continuous development due to their power management efficiency and cost improvements. However, the rate of progress has been decreased in recent years since this technology has almost reached its theoretical limits.

In 1976 power MOSFETs appeared as an enhanced alternative to bipolar transistors. These new devices were introducing important improvements such as an increased ruggedness, faster switching behaviour and the capability of manage larger current levels. This fact gave rise to an important increase and development of the power electronics field and their utilization in different applications, such as desktop computers, variable-speed electric motor drives, DC-DC power supplies, low-voltage (LV) renewable generation, lighting and home appliances, battery chargers, transportation, industry tools and many other applications [3].

One of the most important challenges to overcome in electrical energy conversion consists in reducing as much as possible the power losses of the converters, which directly implies to develop more efficient transistors. Since there is no much more margin to improve the Si devices efficiency, new solutions are being investigated. Other relevant features that must be present in a new semiconductor to be economically viable are: reliability, power density, manufacturability and modularity. Different options can be used as an enhanced alternative to Si power MOSFETs. For high frequency high power applications, Gallium Arsenide (GaAs) devices represent one of the most powerful alternatives. However, they do not satisfy the ever-increasing performance requirements, so there is an emergin interest in other wide band-gap materials and device technologies that inertly satisfy the performance demand thanks to their material properties [44].

Although there are still some improvements to achieve in power MOSFETs (which will reduce the cost of these devices), Gallium Nitride (GaN) transistors are becoming one of the most promising technologies for low and medium voltage power conversion in the following years. This technology offer higher power densities and higher operating efficiencies than power MOSFETs and GaAs devices, and it is expected to become dominant in many commercial and space applications of power devices. In addition, thanks to the AlGaN/GaN heterostructure, the basis for the generation of the high electron mobility transistors (HEMTs) that rely on a two dimensional electron gas (2DEG) for conduction is provided, leading to excellent properties such as increased current density and output power. GaN-based HEMTs are suitable for high power high frequency applications due to their high thermal conductivity, large polarization fields, and saturation drift velocity [34]. The largest operating frequencies achieved with GaN HEMTs are around 94 GHz [33] and highest power densities than 30 W/mm [11]. Furthermore, due to the high breakdown-field, it is possible to use this technology in high-power switching appliances. However, GaN-based devices have not reached yet their maturity for high power high frequencies applications. This technology still has many features to improve and that is why its research and development is on the rise.

## 1.2 Objective of the Thesis and Report Outline

In this thesis, the promising switching power technology of GaN HEMTs will be evaluated in different ways: theoretically, in simulations and experimentally. The objective of this project is to evaluate the switching characteristics of these devices by carrying out different experimental and simulation tests. For this purpose, an evaluation platform of *GaN Systems* will be used in the experimental analyses, as well as a Digital Signal Processor (DSP) of *Texas Instruments*.

The thesis will be constituted by the following chapters:

- Chapter 1: Introduction and report outline.

- Chapter 2: Theoretical analysis of the GaN HEMTs. In this chapter, a theoretical study of the main characteristics of the GaN high electron mobility transistors will be carried out. The principles of operation of these devices will be explained, as well as the device structure, the electrical features, and the driving considerations.

- Chapter 3: During this chapter, a theoretical explanation of the tests that have been performed to analyse the switching characteristics of the GaN transistors will be included. The practical implementation of these tests will be also included, for both the simulation and experimental evaluations.

- Chapter 4: In this chapter, the results of the analyses carried out experimentally and in simulations will be commented, observing the switching characteristics of the power devices and making a comparison between the experimental and simulation results.

- **Chapter 5:** The conclusions of the project and the future work will be included in this chapter.

# Chapter 2

# Gallium-Nitride HEMTs

In this chapter, the main characteristics of the GaN devices will be explained. Particularly, a brief comparison of the material properties of these transistors with respect to Si and SiC technologies will be performed, and later the GaN devices will be studied in more detail, analysing the fundamentals of operation, the device structure, types of GaN devices, the electrical characteristics and the driving features.

### 2.1 Material Properties and Advantages of GaN

As commented in Chapter 1, silicon devices have assumed a central role in the design of semiconductor devices in the last thirty decades. However, they have almost reached their theoretical bounds, due to the Si intrinsic material properties such as low breakdown voltage, low saturation velocity, high device resistance and low inversion layer mobility [2]. For this reason, there is an increasing interest in studying and developing new and improved semiconductor materials to design switching devices.

Wide band-gap semiconductors such as GaN or Silicon Carbide (SiC) represent one of the most promising materials that are able to meet the requirements for highpower, high temperature switching applications. In table 2.1 [34], [37] the main material properties of Si, SiC and GaN semiconductors are exposed:

| Material Property                            | Si   | SiC  | GaN  |

|----------------------------------------------|------|------|------|

| Band Gap $[eV]$                              | 1.12 | 3.26 | 3.39 |

| Critical Breakdown Electric Field [MV/cm]    | 0.23 | 2.2  | 3.0  |

| Electron Mobility $[cm^2/V\text{-sec}]$      | 1350 | 950  | 1500 |

| Electron Saturation Velocity $[10^7 cm/sec]$ | 1.0  | 2.0  | 2.5  |

| Thermal Conductivity [Watts/cm K]            | 1.5  | 3.8  | 1.3  |

Table 2.1: Material properties of Si, SiC and GaN [26]

In this table, the advantages of GaN over its main competitors in the semiconductor market can be observed. The band gap defines the strength of the bonds between the atoms in the lattice, that is, the difficulty for an electron to jump from one site to the next. As it can be checked, GaN and SiC have larger band gaps in comparison with Si. This improves the blocking performance for a given temperature, and provides avalanche rugedness.

It can be seen that GaN has the highest electrical breakdown field (an order of magnitude higher). For a given voltage rating, much higher doping levels can be used, achieving better on-state performance with reduced thickness, which implies less charge accumulation effects and in turn, improved switching characteristics. Conversely, for a given chip thickness, devices with much higher voltage ratings can be achieved.

The electron mobility and saturation velocity are also higher in GaN material, which implies a better conductivity of the devices. This advantage is illustrated in Figure 2.1: for same sized transistors, rated for the same breakdown voltage, as the breakdown voltage increases, the on-resistance increases as well for all de materials, but GaN shows the best performance in this characteristic, achieving the lowest onresistance when comparing the different materials at the same breakdown voltage level.

The large electron sheet densities (around  $1 \times 10^{-13} cm^{-2}$ ) and the high electron mobility also allow to achieve large drain currents of grater than 1 A/mm. However,

Figure 2-1: Theoretical on-resistance vs blocking voltage capability for silicon, siliconcarbide, and gallium nitride [3].

GaN shows a similar thermal conductivity than silicon, which is much lower than that of SiC (over three times lower). This means that the the efficiency to dissipate heat is significantly worse, which implies a better thermal management from part of GaN devices when compared to SiC.

Another remarkable characteristic particular from the wide-band semiconductor materials can be evaluated with the Johnson's Figure of Merit (JFOM). This function gives an idea of the material suitability for high-power high-frequencies applications, and can be calculated by using the following expression [30]:

$$JFOM = \left(\frac{E_c \cdot v_{sat}}{2\pi}\right)^2 \tag{2.1}$$

Table 2.2: Figures of merit of GaN and competing semiconductor materials in power electronics [5].

| Property | $\operatorname{GaN}$ | $\mathbf{Si}$ | GaAs | $\mathbf{SiC}$ |

|----------|----------------------|---------------|------|----------------|

| JFOM     | 270-480              | 1.0           | 2    | 324-400        |

In Table 2.2 the values for the JFOMs for the different semiconductor materials are shown. As it can be observed, the JFOM of the GaN is around 270 to 480 times higher than that of silicon, about 135 to 240 times larger than GaAs and over 1.5 times greater than SiC. In general, wide-band materials offer the best performances to meet the modern-day power electronic requirements. But it is obvious that GaN is the best solution for high-power high-frequencies applications than their market competitors. With all these properties, it can be determined that GaN-based devices are ideal for microwave and millimetre wave amplifiers, RF amplifiers, space and radar electronics including local multipoint distribution systems, digital radio and base station transmitters [5]. In the power electronics field, GaN-based High Electron Mobility Transistors (HEMTs) represent a promising technology for electric and hybrid vehicles, electrical inverters, switched mode power supplies and motor drive circuits which operate in the voltage range of 600 V to around 1200 V [37] [40].

### 2.2 Fundamentals of 2DEG and HEMTs

Due to the aforementioned GaN superior intrinsic physical properties (such as wideband gap, high breakdown electric field, high electron saturation velocity and high density carriers in the form of a 2DEG with high mobility), this material is suitable for high-power high frequencies applications. These devices present great performance improvements, and are also able to operate in harsh environments where silicon transistors cannot work.

An essential property of III-nitride materials (as is the case of GaN) is the capability to form a heterojunction with a ternary alloy made from another III-nitride semiconductor material such as aluminium gallium nitride (AlGaN). Thanks to the strong polar material properties, the modification of the material composition results in dramatic modifications of the polar crystal properties and hence of available carrier concentrations obtained at the heterojunction interfaces in the devices [5]. In this way, a two-dimensional electron gas (2DEG) is formed at the heterojunction, where the electrons are confined to move in two dimensions, in the plane perpendicular to the surface of the device. This represents the conduction channel. Group III-Nitride semiconductors can be found in different common crystal structures. The natural structure of crystalline gallium nitride is a hexagonal structure named "wurtzite" (see Figure 2.2).

Figure 2-2: Schematic of wurtzite GaN [27].

This structure is really robust due to its high chemical stability and it is able to withstand high temperatures without decomposition. Piezoelectric properties are also provided to GaN by this crystal structure which gives the ability of achieving very high conductivity in comparison with other semiconductor materials. As commented before, by using a thin layer of AlGaN on top of a GaN crystal, a strain is created in the interface leading to the 2DEG (see Figure 2.3). Since the total charge must be neutral, the free electrons accumulate in the quantum well to compensate the high positive polarization induced sheet at the AlGaN/GaN interface. The electrons in the quatum create a two dimensional electron gas channel. This effect allows the efficient conduction of electrons when an electric field is applied between its terminals (see Figure 2.4) [6] [51].

Among other reasons, this layer has very good conductive properties due to the concentration of electrons in a very small region at the interface. Thanks to this phenomenon, the mobility of electrons is increased from about  $1000 \, cm^2/Vs$  to  $1500 - cm^2/Vs$ .

Figure 2-3: Simplified cross section of a GaN/AlGaN heterostructure showing the formation of a 2DEG due to the strain-induced polarization at the interface between the two materials [27].

Figure 2-4: By applying a voltage to the 2DEG an electric current is induced in the crystal [27].

$2000 \ cm^2/Vs$  in the 2DEG layer. The high concentration of electrons with very high mobility represents the basis for the high electron mobility transistor (HEMT) [27].

### 2.3 The Basic Device Structure

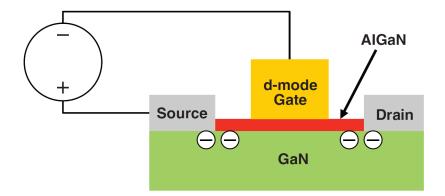

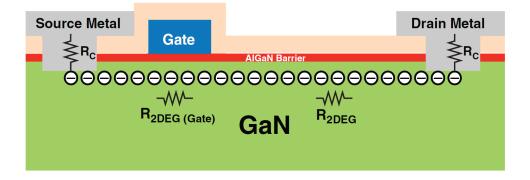

The structure of a GaN power transistors is composed by gate, source and drain terminals. The drain and source electrodes pass though the AlGaN material in order to create an ohmic contact with the 2DEG. This fact allows to conduct current between the drain and source terminals, since a short circuit is created until the 2DEG is depleted. When this occurs, the GaN semiconductor crystal is able to block the current flow. The gate terminal is used and placed over the AlGaN layer to deplete the 2DEG. A negative voltage bias relative to both drain and source terminals should be applied to the gate electrode in order to deplete the electrons from the 2DEG. This is the simplest GaN transistor structure, and is called a depletion-mode or d-mode [27]. Notice that the structure of GaN HEMTs is different from that of the silicon metal-oxide field effect transistors (MOSFETs). The PN junction created from the p-region of the body to n+ region at the drain forms a body diode in a typical Si power MOSFET, which is not present in a GaN HEMT [26]. In the following figure, a representation of the GaN HEMT structure is depicted:

Figure 2-5: By applying a negative voltage to the gate of the device, the electrons in the 2DEG are depleted out of the device. This type of device is called a depletion-mode (d-mode) HEMT [27].

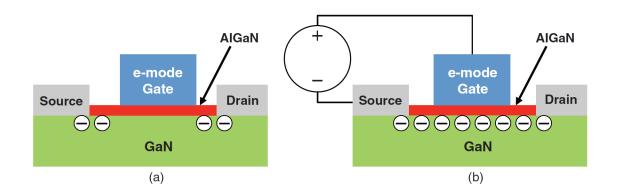

However, d-mode GaN HEMTs are not recommended for power conversion, since a negative bias must be first applied to the transistors at the start-up of the power converter. Otherwise, a short circuit could result. Also, since the normal state of these devices is ON, the lost of the gate drive circuit will maintain the device in on-state, which can lead to short circuits. Instead, other device designs can be used, which have normally off-state devices and a positive threshold voltage is required to turn-on the device. They represent a safer alternative, since the switches would turn-off when the power is lost in the gate drive circuit. Enhancement-mode (e-mode) devices are a good representation of this solution, which will not experience the previously commented issues. When a zero bias is applied to the gate terminal, the e-mode device is OFF (see Figure 2.6 (a)), and will not conduct current until a positive threshold voltage is applied (see Figure 2.6 (b)). There exist different popular structures that have been designed to create an enhancement device, such as the recessed gate, implanted gate and cascode hybrid.

Figure 2-6: (a) An enhancement-mode (e-mode) device depletes the 2DEG with zero volts on the gate. (b) By applying a positive voltage to the gate, the electrons are attracted to the surface, re-establishing the 2DEG [27].

#### 2.3.1 Recessed Gate Enhancement-Mode Structure

The idea of this structure consists in reducing the thickness of the AlGaN barrier over the 2DEG, in such a way that the voltage created by the piezoelectric field is reduced proportionally. When the generated voltage in the AlGaN/GaN interface is lower than the built-in voltage of the Schottky gate barrier, the 2DEG is depleted with a gate zero bias. When a positive bias is applied, the electrons are attracted to such interface and the circuit is closed, therefore allowing the current conduction [24]. One of the most critical aspects to consider in e-mode GaN devices is the small margin of gate voltage. This is due to the fact of the low gate breakdown voltage and the necessary fully turn on voltage is quite close to the gate voltage limit [15].

#### 2.3.2 Implanted Gate Enhancement-Mode Structure

This method, uses an implant of fluorine atoms in the AlGaN barrier layer to create the e-mode device [8]. In order to deplete the 2DEG, the fluorine atoms create a "trapped" negative charge in the AlGaN layer. The enhancement-mode HEMT can be created by using a Schottky gate over the AlGaN interface.

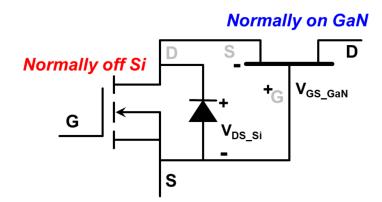

#### 2.3.3 Cascode Hybrid Enhancement-Mode Structure

The particularity that characterises a cascode GaN device is the incorporation of a low-voltage enhancement-mode Si MOSFET in series with a depletion-mode GaN HEMT [16], as shown in Figure 2.7:

Figure 2-7: Cascode configuration combining a high voltage normally on GaN HEMT with a low voltage normally off silicon MOSFET.

With this configuration, when a positive voltage is applied to the gate terminal of the MOSFET to turn it on, the gate voltage of the depletion-mode GaN device downs to near-zero volts and turns-on. Therefore, the current can flow between the drain-to-source GaN transistor terminals and MOSFET. In order to turn the GaN device off, the voltage at the gate MOSFET electrode must be removed. In such situation, a negative voltage is created between the depletion-mode GaN transistor gate and its source terminal, turning the device off. This structure represents a good solution of an enhancement-mode transistor when the GaN device has a relatively high on-resistance compared with the low-voltage Si MOSFET. However, the previously commented e-mode GaN devices present are slightly better than cascode transistors. This is because of the fact that the gate loop inductance is significantly reduced, since no additional MOSFET is required [15].

### 2.4 GaN HEMTs Electrical Characteristics

In this section, the electrical characteristics of GaN transistors to develop power converters will be commented with respect to the features seen in the previous sections. They will also be compared with the traditional Si power MOSFETs, studying their differences and similarities. The main electrical parameters to analyse in a power device are: breakdown voltage between the drain and source electrodes  $(V_{BD})$ , onresistance  $(R_{DS(on)})$  and threshold voltage  $(V_{GS(th)})$ . The parasitic capacitances, as well as the reverse conduction will be also evaluated to provide a complete analysis of the GaN transistor.

#### 2.4.1 Breakdown Voltage $V_{BD}$

The breakdown voltage of a semiconductor material device is defined as the maximum reverse voltage at which can be submitted before it becomes electrically conductive. Particularly, a power transistor will suffer break down when the the critical electric field ( $E_{crit}$ ) of any of the included materials is exceed. In such moment, the device will start to conduct current. Notice that the breakdown voltage between the source and drain electrodes is also influenced by the specific design of the device, the specific heterostructure, the internal insulating layers in the device structure above the gate, source and drain electrodes; and the underlaying subtrate material properties [29].

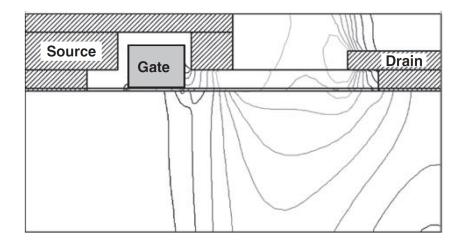

Higher electric fields are created near the drain and gate electrodes, where the contour lines are closer, as shown in Figure 2.8.

The breakdown voltage effect can be also be caused by the interaction between the metal used layers in the device. This phenomenon is produced when one of these layers is connected to the source electrode while a contiguous layer is connected to the drain terminal. In case the  $E_{crit}$  of the dielectric material which separates these

Figure 2-8: The device in Figure 2.6 showing the electric fields when voltage is applied from drain to source.

layers is exceeded, breakdown takes place [27].

The breakdown phenomenon leads to destructive results in HEMTs. Characteristically, if the effect is produced when the insulating layers exceed the critical electric field, the dielectric material will suffer a physical rupture [31]. In case the GaN layer exceeds its critical electric field and breakdown is produced in the GaN or AlGaN layers, a different phenomenon takes place: the generated electrons can destroy the 2DEG, causing the device on-resistance to widely increase [20].

#### **2.4.2** On-Resistance $R_{DS(on)}$

The on-resistance of a semiconductor power transistor defines the conduction losses during the on-state operation [1]. Therefore, it is an essential parameter that requires a proper study and knowledge to optimise the performance of the device and hence of the power conversion system. It is composed by the sum of all the resistance elements that constitutes the device, as shown in Figure 2.9.

As it can be observed, the source and drain electrodes must connect the 2DEG with the AlGaN layer. This resistance component is known as the contact resistance  $(R_c)$ . During conduction, electrons flow in the 2DEG with a certain resistance, called  $R_{2DEG}$ . In the following expression, a description of this resistance is exposed [50]:

Figure 2-9: Cross section of a GaN HEMT, showing the major components of  $R_{DS(on)}$  [27].

$$R_{2DEG} = \frac{L_{2DEG}}{q \times \mu_{2DEG} \times N_{2DEG} \times W_{2DEG}}$$

(2.2)

Where  $L_{2DEG}$  is the distance the electrons have to travel, q represents the universal charge constant  $(1.6 \times 10^{-19} \text{ coulombs})$ ,  $\mu_{2DEG}$  is the electron mobility,  $N_{2DEG}$  represents the number of electrons created by the 2DEG and  $W_{2DEG}$  is the width of the 2DEG. It is known that the number of electrons in the 2DEG is directly dependent on the induced strain in the AlGaN barrier. However, the electron concentration under the gate terminal can be lower than in the area located between the gate and drain electrodes, therefore leading to a different on-resistance component:  $R_{2DEG(Gate)}$ . This depends on the type of gate, the process used, the heterostructure and the applied gate voltage. Hence, an approximation of the transistor resistance can be calculated in the following manner [27]

$$R_{HEMT} = 2 \times R_C + R_{2DEG} + R_{2DEG(Gate)} \tag{2.3}$$

Finally, other parasitic resistances arising from different metal buses that conduct current from the electrodes to the terminals can be consider. Hence, the on-resistance can be calculated with the next equation:

$$R_{DS(on)} = R_{HEMT} + R_{parasitic} \tag{2.4}$$

Notice taht, although the channel and access resistances of AlGaN/GaN HEMTs are minimised by the effect of the high electron mobility provided by the 2DEG, this benefit is only ensured during static bias conditions. When drain current transients from a high-voltage off-state to low-voltage on-state take place, the on-state resistance is normally modified as compared with its static value (the on-resistance remains high for a period of time) [19]. This effect of increased dynamic on-resistance and the adjacent decreased on-state drain current is known as "current collapse", and is considered as one of the most important issues that must be addressed to achieve an efficient power conversion when using GaN-based HEMTs [23].

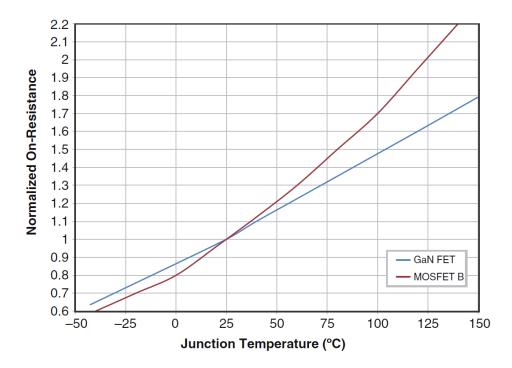

Another important consideration is the variation of  $R_{DS(on)}$  with the temperature. In the following figure, a representation of the variation of the resistance with the temperature is depicted:

Figure 2-10: Normalized  $R_{DS_{ON}}$  vs. temperature for a 100V enhancement-mode GaN transistor (EPC2010) compared with an Si power MOSFET with similar ratings [39].

As it can be observed, the normalised on-resistance is increased with the temperature for both, a GaN transistor and a power Si MOSFET. It can be seen that for temperatures below  $25^{\circ}C$  the MOSFET has lower on-resistance, but for higher temperatures, the GaN device shows a lower  $R_{DS(on)}$  value. It is also remarkable the lower variation with temperature of the resistance in case of the GaN device in comparison with the MOSFET. The reason why GaN transistors are much faster than MOSFETs lies in the fact that the theoretical on-resistance versus blocking voltage of GaN devices is at least three orders of magnitude lower than that of silicon [4].

#### 2.4.3 Threshold Voltage $V_{th}$

As commented previously, the gate electrode is used to generate a Schottky barrier in GaN HEMTs which is able to control the carrier concentration in the channel layer below the interface. As the applied gate voltage decreases, the concentration of carriers below the gate terminal is decreased as well [13]. The threshold voltage for a power transistor is defined as the minimum gate-to-source voltage which is required to create a conducting path between the drain and source electrodes. That is, the required voltage level to turn-on the device.

Below the threshold voltage, the channel remains depleted of carriers, therefore blocking the current to flow between the drain and source electrodes. In case of a depletion mode HEMT, the threshold voltage is negative, and for enhancement-mode HEMT a positive threshold voltage is required.

The threshold voltage in GaN devices is produced when the 2DEG layer below the gate is completly depleted due to the voltage generated by the gate terminal. This phenomenon occurs when the voltage of the gate equals the volatge created by the piezoelctric strain in the AlGaN/GaN barrier. This voltage is composed by the voltage applied externally to the gate  $(V_{th})$  and the built-in voltage (produced by the characteristics of the gate material composition). Usually, the  $V_{th}$  of the AlGaN/GaN HEMTs depends on the epitaxial structure design (known as the Al composition), the doping concentration and the thickness of the AlGaN barrier [9]. Some mechanisms can be used to further modify the threshold voltage during the manufacturing process of the device, as for instance use a fluorine-based plasma treatment [7], where no change in AlGaN thickness is required and no reduction of the 2DEG density is produced. The threshold voltage for enhancement-mode GaN transistors is lower than that of Si MOSFETs. This fact is due to the almost flat relationship between the temperature and the  $V_{th}$  together with the very low gate to drain capacitance. The device can start to conduct at low voltage levels, so care must be taken to prevent mis-operation caused by noise.

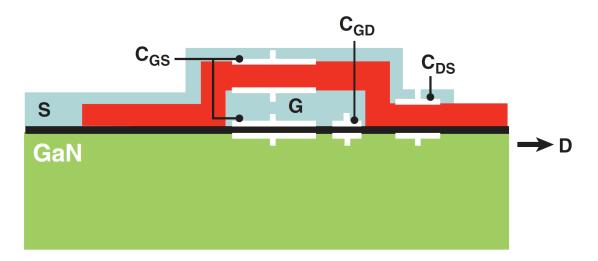

#### 2.4.4 Parasitic Capacitances

The capacitances are used to determine the amount of charge that must be provided to the device terminals to change the voltage of the terminals. In fact, the amount of charge stored in the capacitor can be calculated by integrating the capacitance between the two terminals across the range of voltage applied to such terminals [27]. Therefore, the parasitic capacitances of a power transistor constitute an essential factor when analysing the energy required to turn-on or turn-off the device.

It can be distinguish three main different capacitances in GaN HEMTs: the gateto-source capacitance  $C_{GS}$ , the gate-to-drain capacitance  $C_{GD}$  (also known as  $C_{RSS}$ ) and the drain-to-source capacitance  $C_{DS}$ . A physical representation of these parasitics are depicted in the following figure:

Figure 2-11: Schematic of GaN transistor capacitive sources [27].

It is normally interesting for the design and analysis of devices to group the capac-

itances in the input and output terminals:  $C_{ISS} = C_{GD} + C_{GS}$  and  $C_{OSS} = C_{GD} + C_{DS}$ (respectively). The gate-to-source  $(Q_{GS})$  and gate-to-drain  $(Q_{GD})$  charges are also of special interest since they are directly related with the device switching speed. There exists a parameter to analyse this effect: the Miller ratio, which is the quotient between  $(Q_{GD})$  and  $(Q_{GD})$ . With this simple calculation it is possible to define the voltage at which the transistor will turn on.

Generally, the Si MOSFETs have larger parasitic capacitances than GaN devices. Normally, figures of merit (FOMs) consisting on the  $R_{DS} \times Q_G$  are employed for comparing different MOSFET technologies with the GaN power devices. The results obtained show improvements of three to seven times.

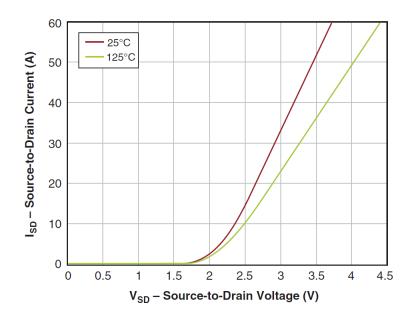

#### 2.4.5 Reverse Conduction of HEMTs

An interesting property of enhancement-mode GaN systems is the fact that they are naturally capable to conduct current in the opposite direction in the absence of a body diode [41]. This natural "body diode" effect and its variation with the drain current can be appreciated in the following figure:

Figure 2-12: Body-diode forward drop vs. source-drain current and temperature by EPC2010 [39].

The condition for this phenomenon to occur is that the drain voltage must be higher than the gate voltage by at least the threshold voltage [27]. If this condition is satisfied, the 2DEG is restored under the gate channel (the 2DEG is turned on), and the current is able to flow from source to drain. Due to this fact, the forward voltage drop will vary with temperature. Notice that, if the gate voltage is decreased below 0 V, the forward voltage drop will augment proportionally.

Another significant parameter is the amount of charge which is dissipated when a body diode is turned on  $(Q_{RR})$ . Since e-mode HEMTs has no minority carrier conduction, the transistor will turn-off just when the forward bias between the gate and drain channels is removed. Therefore, there will not be reverse recovery losses. This feature can be really interesting in some power conversion applications, especially when comparing GaN HEMTs with Si power MOSFETs: the natural body diode has higher voltage drop but no reverse recovery charge relative to Si [38].

## 2.5 Gate Drive Voltage Considerations

As commented in previous sections, the control of the device (either for e-mode transistors or cascode configuration) is achieved by supplying or removing the gate charge from the gate electrode. Driving a cascode device is identical of driving a Si device. Even so, the technique for driving e-mode devices differs in some aspects and requires special considerations. The most important considerations are [14]:

- Low gate threshold voltage.

- Very small margin of applicable gate voltage.

- Parasitic effects.

- Layout considerations.

- dV/dt and dI/dt constraints.

Typically, for e-mode devices, the maximum gate-to-source voltage  $(V_{GS})$  is not greater than 6V, and around just 3V - 4V are necessary to fully turn the device on, which lead to a very small margin. Therefore, gate voltage ringing must be avoided, so device breakdown will not ocur. An important phenomenon is the presence of stray elements in the circuit, which can lead to oscillations on the gate voltage, particularly if there is a common loop inductance between the gate and power loops. To solve this effect, GaN manufacturers provide e-HEMTs packages with kelvin connections for the gate loop, effectively reducing or removing the common inductance. In contrast, cascode devices (which use a Si MOSFET to achieve normally off state behaviour) can be driven with around 20V. On the other hand, the threshold voltage of the GaN is very low (1 - 2V), leading to the risk of unintentional turn-on of the transistor when the device is used in high dV/dt applications [10]. These gate voltage issues can be addressed by critical damping the gate-drive turn-on of the switching power loop. Notice that the turn-on and turn-off actions are different processes, so different damping requirements are necessary for each activity (use of independent gate resistors to adjust the turn-on and turn-off gate loop damping). In the Figure 2.13, a representation of the gate voltage versus time is included.

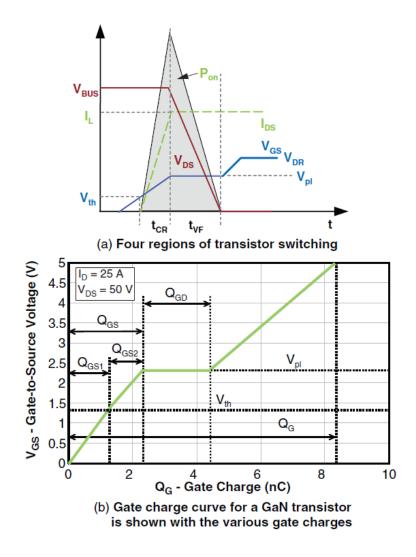

As it can be observed, different charge components are present. Particularly, four regions can be appreciated:

- 1. The charge required to bring the gate electrode up to the device threshold voltage, which will cause the drain-to-source current to start flowing (start of conduction).

- 2. The necessary charge to complete the current rise transition time  $(t_{CR})$  and reach the Miller plateau voltage  $(V_{pl})$ .

- 3. The charge supplied to complete the voltage transition time  $(t_{VF})$ . The current provided to the gate terminal is used to discharge the gate-to-drain parasitic capacitance  $(C_G D)$ , almost no current is used to charge the gate-to-source parasitic capacitance  $(C_{GS})$ . As a consequence, the Miller plateau appears.

- 4. The charge required to drive the gate to steady-state gate voltage.

Figure 2-13: Gate charge vs. gate voltage showing different gate charge components for an EPC2010 GaN transistor [39].

Therefore, as Figure 3.13 shows, it can be noticed that the switching speed is dependent on the gate-to-source and gate-to-drain capacitances. The following modifications are expected in the switching waveform if the gate-to-source capacitance is increased [42]:

- An increase in the turn-on and turn-off delay between driver input and device output, as the time to charge the capacitor to reach the threshold voltage will last longer.

- Increased turn-on and turn-off time for the device drain current, since the time

to charge the capacitor to reach the Miller plateu from the threshold value will be increased as well.

• Increased operating time with increased on-state resistance, since it takes longer time to charge the capacitor from the plateau voltage to the steady-state value.

In the following table, a comparison of the gate characteristics of the GaN E-HEMTs with respect to Si MOSFETs, IGBTs and SiC MOSFETs is exposed:

Table 2.3: Gate drive voltages for GaN HEMTs, Si MOSFET, IGBT and SiC MOS-FEt [48].

| Gate drive voltage level | GaN HEMT | Si MOSFET | IGBT   | SiC MOSFET |

|--------------------------|----------|-----------|--------|------------|

| Maximum rating           | -10/+7V  | +/-20     | +/-20V | -8/+18V    |

| Transient maximum        | -20/+10V |           | +/-30V |            |

As it can be checked, the gate voltages used to drive GaN HEMTs are different with respect to the technologies compared. A lower gate drive voltage is required, as commented before, with a lower voltage transient with respect to other technologies. The negative gate voltage in GaN HEMTs improves gate drive robustness but is optional. On the other hand, a much smaller gate-charge is required in GaN devices, since they do not have parasitic body diode, which implies lower drive losses, and faster rise and fall time.

# Chapter 3

# Theoretical Frame of the Analyses

In this chapter, the analyses performed to study the GaN devices experimentally and in simulation will be explained. In this project, the double-pulse test was used to analyse the GaN HEMT performance, and a synchronous-buck converter was used to test such devices in a real application. The initial idea was to perform more tests in other converter topologies, but due to the setbacks produced during the experiments it was not possible to carry out more analyses. The practical implementation of the performed tests will be also explained in this chapter.

## 3.1 Double-Pulse Test

#### 3.1.1 Theoretical Background of the Double-Pulse Test

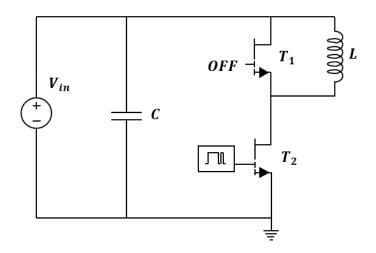

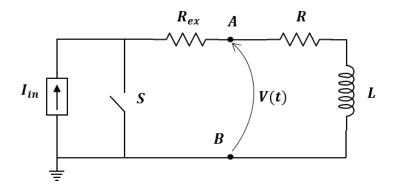

In order to analyse the switching transients and the switching power losses of the GaN transistors, the double-pulse test (DPT) has been used. The circuit used to perform this test is mainly composed by two power transistors, a DC voltage source (with a parallel capacitor) and an inductor as the load. This configuration is shown in the following figure:

Figure 3-1: Double-pulse test circuit - Inductive load.

In this test, the upper transistor will be used to perform the function of a diode, since these devices do not need an anti-parallel diode. This means that the switching commands to the gate terminal of this transistor will never be forward biased, but reverse or no biased, depending on the E-HEMT desired operation (explained in Section 2.3).

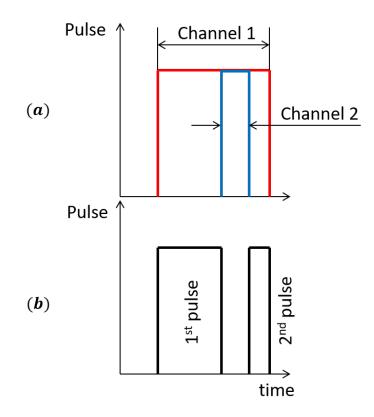

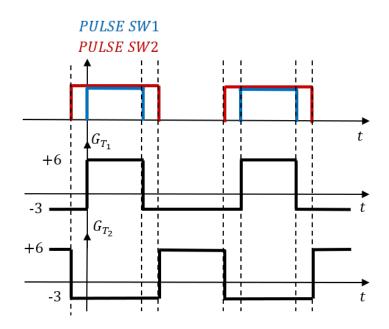

The test is carried out acting on the lower device, just by using two pulses of different duration, therefore avoiding heating the device. The first pulse is used to increase the current through the load up to the desired test level, and thus be able to analyse the transistor turn-off behaviour at the end of this pulse. Then, a break is produced to give way for a second pulse, which is used to study the transistor turn-on. Notice that the sequence to perform this test must be large enough to provide time for the inductor to discharge, otherwise the load current could increase and damage the components. The ideal pulse waveform to perform the DPT is depicted in the Figure 3.2.

As it can be observed, the first pulse is a wide pulse used to charge the inductor, therefore reaching the desired current level to analyse the turn-on, while the second pulse is used to analyse the turn-off, so it is thinner. To reach the test current, it will be necessary to properly adjust the width of the first pulse commanded to the gate channel.

Figure 3-2: Double-pulse test signals - Inductive load.

#### 3.1.2 Simulation Implementation of the Double-Pulse Test

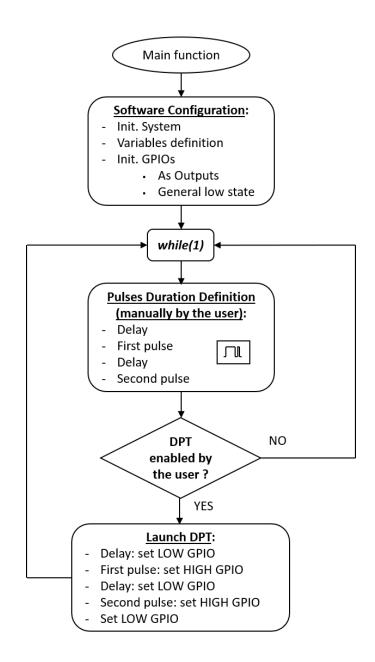

For the simulation implementation of the double-pulse test, the power electronics software  $PSIM(\mathbb{R})$  (Version 11.1.3) has been used. Thanks to the latest improvements of this program, it is possible to model, simulate and evaluate the performance of real devices. This is possible due to the interface connection together with the simulating power devices software  $LTSpice(\mathbb{R})$  (Version XVII).

Different voltage waveforms have been used in order to create the different pulses (with their respective duration) to apply to the gate terminal. In the analyses, the first pulse duration has been varied for each test with the purpose of evaluating the switching transients during the turn-on and turn-off of the GaN device at different current levels. Particularly, the evaluated current values are comprised between 5 A to 30 A in steps of 5 A. Alternatively, the input voltage has been varied from 50 V to 300 V in steps of 50 V. In this way, for each evaluated voltage level, all the previously mentioned current values have been tested.

The key aspect of these analyses relies in the fact of using close-to-reality power devices. In the manufacturer web-page of the experimentally used GaN devices (GaN Systems) there are available the transistor SPICE models that allow the user to perform close-to-reality tests. As commented before, the characteristics provided in this files can be now used in PSIM in a similar way than in LTSpice. The user can easily create a subsystem to model the desired GaN transistor and link the required

characteristics to such subsystem by using a LTSpice netlist with all the required information.

As it can be observed in Figure 3.1, the upper power device is a GaN transistor too. In this case, such device is performing the function of the diode used typically in DPTs. As commented in previous sections, GaN devices do not have body diode, but thanks to the 2DEG they are able to conduct reverse current. Therefore, this upper transistor does not need to be driven by any gate voltage signal.

It is also important to include in the simulation model the parasitic elements that may have the mother board (PCB) used in the experimental results. In this case, the parasitic inductances have been included following the example available in the GaN Systems web-page of a double-pulse test simulation [45]. The rest of the parameters of the simulation have been selected according with the DPT implemented in the data sheet of the module used. They are described in the following table:

| Parameter             | Value  |

|-----------------------|--------|

| $V_{test}$ [V]        | 50-300 |

| $I_{test}$ [A]        | 5-30   |

| $L_{test} \ [\mu H]$  | 120    |

| $R_{G_{ON}}[\Omega]$  | 10     |

| $R_{G_{OFF}}[\Omega]$ | 2      |

| $V_{GS}$ [V]          | +6/-3  |

| $L_G [nH]$            | 0.5    |

| $L_{CS}$ [nH]         | 3      |

Table 3.1: Parameters used for the DPT simulations.

#### 3.1.3 Experimental Implementation of the Double-Pulse Test

To perform the double-pulse test experimentally, the GS66508T/GS66516T-EVBDBGaN E-HEMT Daughter Board and the GS665MB-EVB Evaluation Platform was planned to be used at first. After performing the first test, at the lowest voltage level, one of the power transistors exploded for no apparent reason. In fact, the pulses had not been commanded to the switches, only the DC-link voltage was activated, as well as the motherboard to power-up the drivers and the fan to cool the transistor. One of the main characteristics of this kit relies in the fact that, the daughter board (where the transistors are placed) can be easily removed from the motherboard, as shown in the following figure:

Figure 3-3: (a) GS66508T/GS66516T-EVBDB GaN E-HEMT top side daughter board 650V. (b) GS665MB-EVB Evaluation Platform.

This feature allowed us to replace the damaged power transistor by a new and workable device. After that, all the conditions to perform the test again were examined in depth to avoid any type of failure: the pulses generated for the test, the connections from the pulses to the experimental kit, the DC-link voltage source, etc. However, this new device suffered the same issue than in the first case, it blew up in a similar way, just after power-up the motherboard and the DC-link voltage, but before commanding the pulses to the switches. At this point, it was clear that we had an issue somewhere in the assembly that had to be solved to perform the DPTs.

In the following figure, a scheme of the circuit that we had in the situation on which the transistors exploded is depicted:

Figure 3-4: First assembly used to perform the double-pulse test.

As commented previously, there was no apparent reason for any of the transistors to suffer a failure before commanding the pulses, since an open circuit was produced, so no current could flow through the devices. After some days trying to investigate and identify the possible causes that could produce a fail that made the transistors to explode, it was found that, a critical point was the interconnection between the evaluation platform (where the transistors are located) and the motherboard (where the drivers and power circuit are placed). It was observed that such connection was really poor, since the evaluation platform and the motherboard were not firmly attached to each other. In fact, if the user touched the evaluation platform, it could be physically disconnected from the mother board. Of course, this fact supposed a huge problem, since the control is commanded to the motherboard and then, this signals are transmitted to the evaluation platform (and hence, to the devices) by means of a set of pins with a really unreliable, poor and dangerous conditions. This situation is shown in Figure 3.5.

From this circumstances, we noticed that the commanded pulses to the transistors could not be transmitted properly. It was highly likely that the switch was closed when the board was powered-up, thus creating a short-circuit and explaining the explosion of the device.

Figure 3-5: Poor pin connectors used to transmit the control signals from the mother board (connected with the pulse source generator) to the daugther board.

Since this fact was a problem of the evaluation kit provided by the manufacturer and no easy solution was possible, we decided to contact the manufacturer commenting this issue, and to use another evaluation board for this test.

#### **Experimental Evaluation Kit**

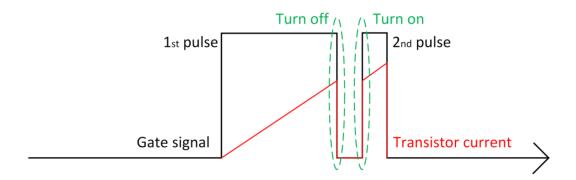

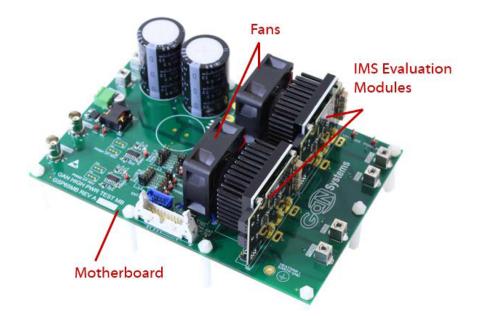

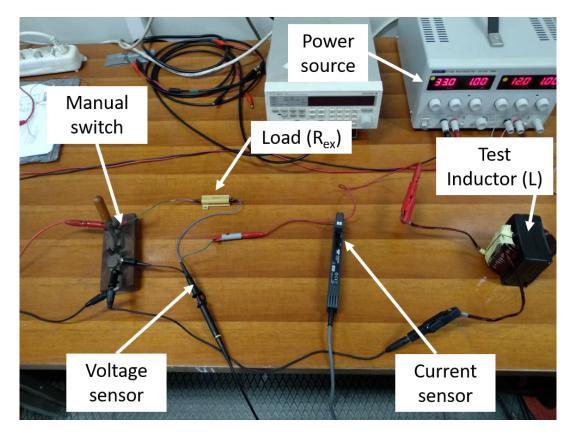

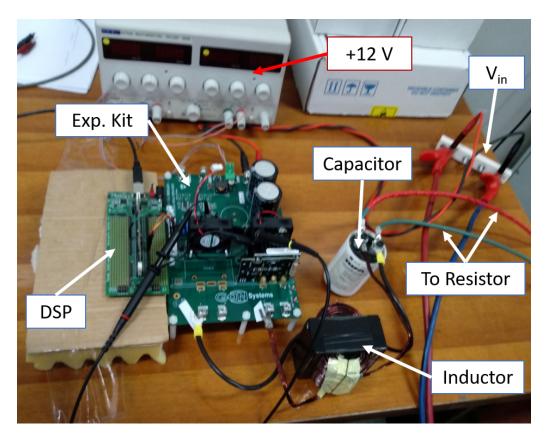

To experimentally carry out the double-pulse test, the high power Insulated Metal Substrate (IMS) Evaluation Platform (from *GaN Systems*) and its corresponding motherboard GSP65HB-EVB was finally used. In the Figure 3.6, a representation of this kit is exposed.

This evaluation kit aims to provide good power density while simultaneously reducing the cost of the system. The IMS platform is used to cool the GaN Systems' bottom-side cooled power transistors. An IMS PCB is also known as Metal Core/Aluminum PCB [47]. This approach has been successfully used in automotive applications, industrial uses or energy storage systems.

As commented before, this evaluation platform consists up of a motherboard and two IMS evaluation modules, where the power devices are located. Each module is configured as a half-bridge and have a power rating of 4-7 kW. Therefore, by using

Figure 3-6: Experimental Evaluation Kit: GSP65RxxHB evaluation motherboard and 650V high power insulated metal substrate (IMS) evaluation modules.

the two modules it is possible to get a full-bridge configuration.

The used IMS evaluation module has the GaN E-HEMT rated at 650 V. The embedded GaN SMD package has the following features [47]:

- Dual symmetrical gate and source sense (kelvin source) for flexible PCB layout and paralleling.

- Large power source/thermal pad for improved thermal dissipation.

- Bottom-side cooled packaging for conventional PCB or advanced IMS/Cu inlay thermal design.

- Ultra-low inductance for high frequency switching.

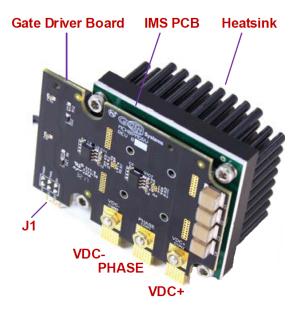

The IMS evaluation module is composed by the GaN E-HEMTs, the gate drivers, the isolated DC/DC supply, the DC bus decoupling capacitors and a heatsink to form a fully functional half-bridge power stage. These modules are attached to the motherboard by using a vertical design concept (as shown in Figure 3.6), therefore achieving high power density. The IMS board uses metal as the PCB core, typically aluminium. A dielectric layer and copper foil layers are bonded to the core. This configuration is shown in Figure 3.7, and it is commonly used in high power applications and high current applications where most heat is concentrated in a small footprint SMT device, since it offers superior thermal conductivity.

Figure 3-7: Insulated metal substrate (IMS) evaluation module used in the motherboard.

Since GaN technology is being adopted widely, the industry is trying to avoid through-holes (TH) packaging, and introducing surface mount packaging (SMT), as is the case of this manufacturer. Traditional TH devices produce high parasitic inductances and capacitances that can be avoided with SMT components, achieving better performances. These packages offer low inductance and low thermal impedance, enabling efficient designs at high power and switching frequencies.

In SMT devices, the thermal management must be approached differently than in TH transistors. In the latter case, the packages are cooled by attaching them to a heatsink, with an intermediary Thermal Interface Material (TIM) layer of electrical high voltage insulation. On the contrary, SMT power devices are cooled by using thermal vias tied to multiple copper sheets in a PCB. The IMS board presents another option which achieves a much lower junction to heatsink thermal resistance thanks to the design commented in the previous paragraph. This fact allows a more efficient heat transfer out of the transistor, and is suitable for SMD devices intended for high power applications.

Other important characteristics of the module are described below:

- The half-bridge configuration (one leg composed by two transistors) is designed in a two-board assembly in order to address the drawbacks of implementing the design on a single layer IMS board. The gate drive circuitry is mounted on a multi-layer FR4 glass-reinforced epoxy material. On this PCB, the gate drivers ICs are included, as well as the isolated DC/DC converter to power the driver IC, and DC decoupling capacitors. On the contrary, the GaN E-HEMTs are assembled on the IMS board.

- To attach the IMS board to the FR4 driver board, small pitch low profile SMT headers are used. The short loop lengths reduce the parasitic gate inductances.

- It is well known that a large copper area helps to maximise the heat transfer to cool the devices, but the area of copper at the switch node (high dv/dt) needs to be minimised to reduce the parasitic coupling capacitances to the metal substrate. An IMS board with thicker dielectric layer was chosen to reduce this effect.

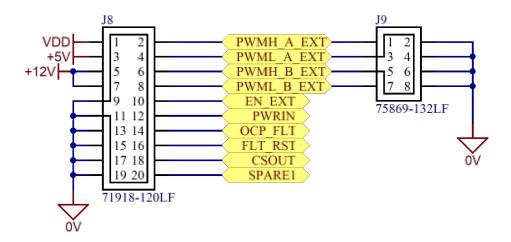

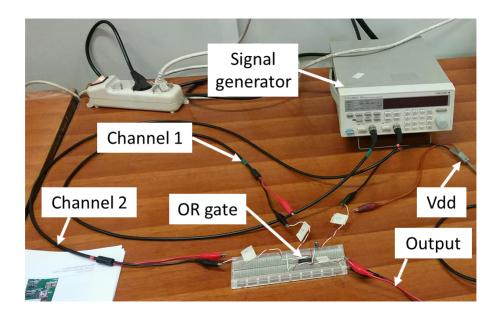

Another important feature of the experimental kit is the external PWM and control Input/Output (see Figure 3.8). As it can be seen, the PWM pulses can be commanded to the motherboard by two different mechanisms:

- PWM Input: In this case, the PWM pulses are commanded to the power devices by means of an external signal generator source. As it can be observed in the figure, there is also an integrated circuit responsible for the dead-time generation between transistors of the same leg. The duration of the dead-times in this case is controlled by selecting the value of a resistor included in the assembly.

- External PWM and control Input/Output (I/O): This pins control different functionalities of the board by means of an external DSP. As it can be observed

Figure 3-8: Pin connectors used to transmit the pulse signals to the gate drivers of the GaN HEMTs from the motherboard to the IMS.

in Figure 3.8, it includes the control of the PWM signals, the enable of these signals, current sense control, over current protection control, etc. For this project, just the PWM signals and the enable will be used.

In the case of the external PWM and control I/O pins, an interface between this ports and the DSP was necessary. The optimal solution would have been to use optical fiber to transmit the PWM and control signals from the DSP to the evaluation kit. However, this material was not available in the laboratory, so other solution was necessary. The most suitable solution with the available material was to use thin cables connected at the output pins of the DSP through individual headers for each cable, and connected to the motherboard by a female connector for the 20 pin header.

Notice that, to prepare the cables for this interconnection, it was necessary to first remove the insulator at both extremes of the cable, then to place the conductive header at the bare part and press it to attach it to the cable, and finally to place an insulator in the header part (attached by applying heat) to avoid electric contact between pins which could produce a short-circuit.

Unfortunately, when the PWM signals were checked in the motherboard (without powering-up the assembly), it was noticed that the PWM commands did not provide required dead-times and shapes due to the increased inductance created by these thin cables to transmit the gate commands. Therefore, the length of them was highly reduced, minimising the distance between the DSP and the gate drive circuit. Even so, the optimal solution would have been to use optical fiber, as explained before.

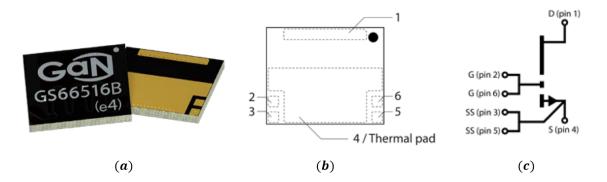

#### 3.1.4 Characteristics of the GS66516B HEMTs

As commented before, the used GaN High Electron Mobility Transistors are provided by the manufacturer GaN Systems. In the following table, the main characteristics of these devices are presented:

| Table 3.2: Parameters used for the DPT simulations. |         |  |  |  |

|-----------------------------------------------------|---------|--|--|--|

| Parameter                                           | Value   |  |  |  |

| Rated voltage $[V]$                                 | 650     |  |  |  |

| Rated current $(I_{DS_{max}})$ [A]                  | 30      |  |  |  |

| $R_{DS_{ON}} \ [m\Omega]$                           | 25      |  |  |  |

| $V_{GS}$ [V]                                        | +6/-3   |  |  |  |

| Transient tolerant gate drive $[V]$                 | -20/+10 |  |  |  |

| Very high switching freq [MHz]                      | > 10    |  |  |  |

| Small PCB footprint $[mm^2]$                        | 11 x 9  |  |  |  |

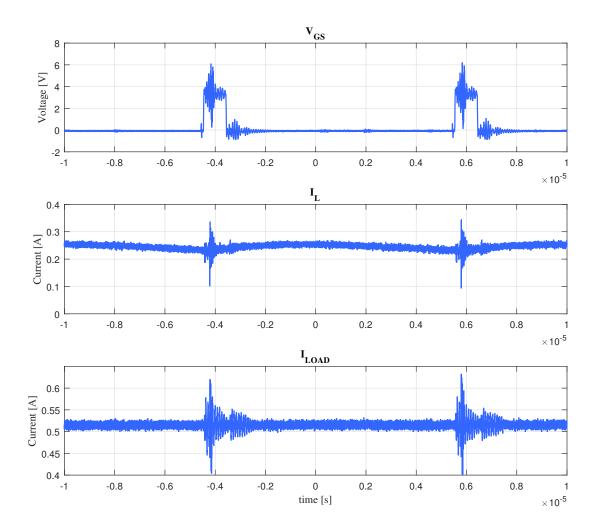

As it can be observed in Figure 3.9, these power transistors use a smd technology. They are enhanced mode gallium nitride (GaN) on silicon power transistors. The properties of GaN allow for high current, high voltage breakdown and high switching frequency. The used small packages enable low inductance and low thermal resistance. Thus, device is a bottom-side cooled transistor which offers a very low junction-tocase thermal resistance for high power demand applications [46]. This combination of features allows to achieve very high power switching efficiency. Furthermore, no wire bond is used, so high reliability is achieved.

Figure 3-9: (a) SMD package for the used GaN HEMTs. (b) Terminals of the used GaN HEMTs in relation with (c), which shows the electrical symbol representation of the transistor.

In practice, these components are suitable for the following applications: high efficiency power conversion, high density power conversion, AC/DC converters, synchronous buck or boost converters, uninterruptible power supplies, industrial motor drives, solar and wind power, fast battery charging, traction drives, etc.

#### Gate Drive

In order to achieve an optimal  $R_{DS(on)}$  and a long live, the recommended gate drive voltage is 0 V to 6 V. The gate drive is able to withstand transients up to +10 V and -20 V for pulses up to 1  $\mu s$ . If 6 V gate drive voltage is used, the enhancement mode high electron mobility transistor (E-HEMT) is fully achieved and reaches its optimal efficiency. Lower voltage can lead to a lower efficiency. GaN systems do not require negative gate bias (as commented in Chapter 2) to turn-off. Negative gate bias ensures safe operation against the voltage spike on the gate, however it increases the reverse conduction loss [46]. Gate drivers with low impedance and high peak current are recommended for fast switching speed. An external gate resistor can be used to control the switching speed and slew rate.

#### Parallel Operation

In the case of these devices, special care must be considered in the driver circuit and PCB layout since the device switches at very high speeds (high dv/dt). It is recommend to design a symmetric PCB layout and equal gate drive loop length on all parallel devices to ensure balanced dynamic current sharing.

#### Source Sensing

This device has two dedicated source sense pads. The used package utilizes no wire bonds, so the source connection results in a very low inductance. Remember that, the common source inductance causes gate ringing and gate oscillations, and it is produced after the source terminal of the transistor. The dedicated source sense pin enhances the performance by eliminating the common source inductance if a dedicated drive signal kelvin connection is created [46]. This can be achieved by connecting the gate drive signal from the driver to the gate pad on the GS66516B and returning the source sense pad on the GS66516B to the driver ground reference.

#### Thermal

The substrate of these components is internally connected to the source/thermal pad on the bottom-side of the GS66516B. The design of the transistor aims to cool the device by using the printed circuit board. The drain pad is not as thermally conductive as the thermal pad. Even so, adding more copper under the drain pad will improve the thermal performance, since the package temperature is reduced.

#### **Reverse Conduction**

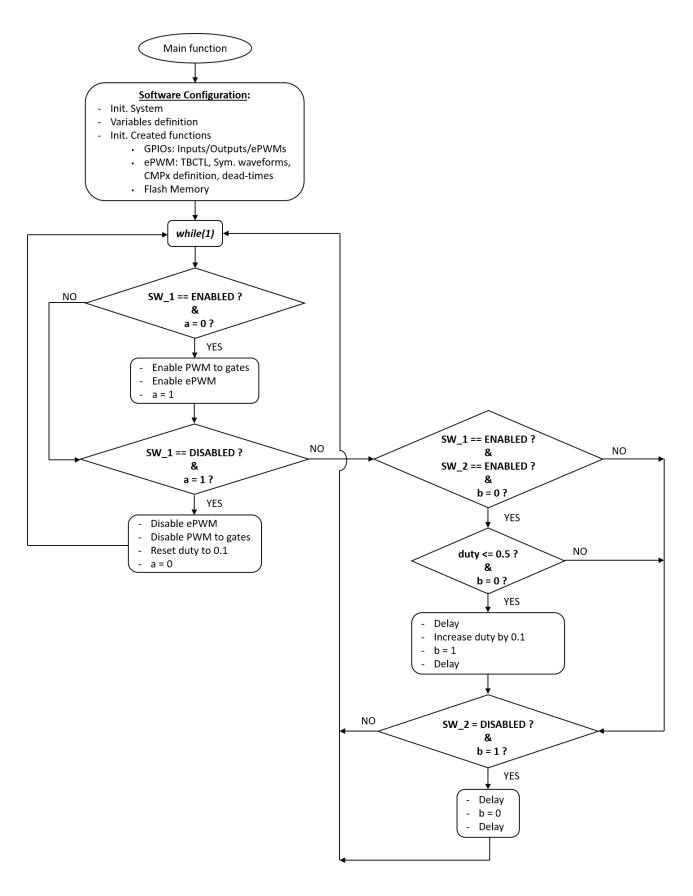

As commented in previous sections, GaN HEMTs do not have intrinsic body diode. However, they are naturally able to provide reverse conduction and exhibit different features depending on the gate voltage: